新式DRAM存取技术倍增超频性能

本文作者曾经为电脑主机板製造公司撰写关于自动超频(overclock)的BIOS,发现微处理器由于受限于主记忆体的性能而必须降低时脉频率来维持电脑系统的稳定性,因而探索一种可提升DRAM单元存取速度的新技术。

无疑地,微处理器的时脉频率可以透过许多方式大幅增加,但却受限于主记忆体的性能而必须降低其时脉频率来维持电脑系统的稳定性。本文透过对于静态随机存取记忆体(SRAM)单元缩减佈局面积的研究,提出一种新的存取技术,可望提升动态随机存取记忆体(DRAM)单元的存取速度。

超频与记忆体的关联性

提升供应电压以及降低环境温度有助于增加微处理器、晶片组、主记忆体的时脉频率,这是对于电脑系统执行超频(overclock)的实体特性;微处理器、晶片组、主记忆体、主机板的整体电路设计,则是用于执行超频的硬体特性。此外,维持作业系统(OS)以及应用程式在执行时的稳定性,是在超频之后的软体特性。

在超频进行中,某些应用程式会有频繁的数学计算以及大量的资料存取,这时可能发生超过晶粒封装材料或外部散热装置的散热效率,因此需要自动超频的技术来监视系统以及调整时脉频率。另一种自动超频是为了确认哪些安装在主机板上的微处理器、晶片组、主记忆体搭配的外部散热装置能够达到超频极限。当基本输入输出系统(BIOS)的程式码加入这一自动超频的功能时,个人电脑(PC)就不必进入OS,也就是不必接上任何磁碟机,就能迅速获得超频的极限值,并且减少磁碟机的磨损。

由于微处理器对于週边装置的资料存取会透过主记忆体来处理,所以主记忆体的稳定性影响着微处理器的执行,即使能够对微处理器进行超频也必须拥有可配合大幅超频的主记忆体,这就是超频记忆体模组的用途。

资料传输介面

单倍资料速率同步动态随机存取记忆体(SDR SDRAM)资料传输介面主要针对DRAM的存取特性,因为DRAM需要经由更新作业来维持储存状态,并且在读取期间需要额外执行回写作业;虽然在写入期间没有额外的作业,但也需要一段时间才能完成储存,这也相当于执行回写作业的时间。由于DRAM的写入以及回写时间皆远大于高速微处理器内部的时脉时间,所以SDRAM根据这样的存取特性而设计资料传输介面的各种讯号与作业程序。SDRAM在发展至双倍资料速率(DDR)之后的性能价格比皆优于其它资料传输介面(如Rambus DRAM;RDRAM)。如今,DDR SDRAM又区分为标準型以及行动型。

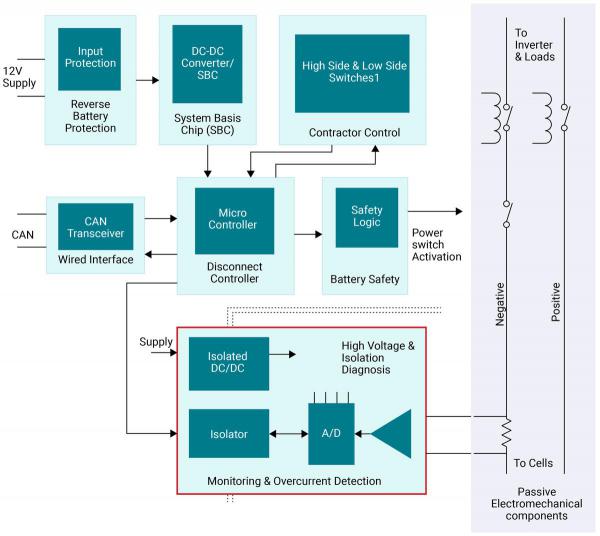

图1显示SDRAM的简要功能方块图,行位址选通讯号(CAS#)是根据预充电而设计的延迟控制讯号,亦即无预充电则不必分时控制列位址选通讯号(RAS#)、CAS#。差动时脉讯号(CLK, CKE)的频率是基于微处理器的工作时脉,资料遮罩讯号(DQM)对应差动时脉讯号的边缘;这些讯号用于进行同步传输作业。对于感测放大器以及写入驱动器的配置规划,通常根据外部资料匯流排的位元宽度而设计相同的数量,然而,可以导入平行存取的方法来增加存取效率,因此增加了行位址的位元宽度以选择同列不同行的感测放大器与写入驱动器。这种方法产生了丛发模式(burst mode)以及同列存取,但并不会增加存取速度,并且还要进行同步传输作业,所以需要资料暂存器。

图1:SDRAM的简要功能方块图

图2显示SDRAM的命令序列,主要参考美光科技(Micron Technology)产品型号为MT48H8M16LF (Mobile SDRAM)的规格表而来。在各命令序列之中,最单纯的命令序列是单一读取以及单一写入,由此可清楚SDRAM的基本作业规则。在图中所表现的命令序列是先执行预充电(PRE),然后活化(ACT),最后执行读取或写入存取(RD或WR),如此循环。

图2:SDRAM的命令序列:单一读取或单一写入

图中,时脉时间(tCK)是从此次时脉边缘至下次时脉边缘为止的时间。列位址选通预充电时间(tRP)是从PRE命令至ACT命令为止的时间。列位址选通至行位址选通延迟(tRCD)是从ACT命令至RD命令或WR命令为止的时间。行位址选通潜伏(CL)是从RD命令开始等候一段时间,并且以tCK为基本单位,然后乘上倍数。写入时间(tWR)是从WR命令至PRE命令为止的时间;另外还可以tCK为基本单位,然后乘上倍数,如同行位址选通潜伏的计时方法,因此命名为行位址选通写入潜伏(CWL)。列位址选通时间(tRAS)是从ACT命令至PRE命令为止的时间。更新命令时期(tRC)是从这次ACT命令至下次ACT命令为止的时间。

DDR SDRAM在PC上的主要设定参数是tRP、tRCD和CL。对于超频记忆体模组的性能则要额外考虑时脉时间与写入时间的最小值,另外就是供应电压的最大值。

资料传输介面的存取效率

SDRAM的存取效率来自丛发模式以及同列存取,并且由此达到资料传输介面的传输速度。如果要频繁进入同列存取那么还要在软体层级之上对资料结构与资料处理进行最佳化的安排;关于资料结构的最佳化像是先分析会被频繁存取的资料栏位,然后将这些资料栏位合併在同一资料结构,使得这些资料栏位可以储存在主记忆体内部的相同列位址;关于资料处理的最佳化像是减少同时对不同资料结构进行交互运算以及交叉存取。

如果发生丛发模式以及同列存取的机率太低,那么存取效率会大打折扣,并且资料传输介面的传输速度会低于DRAM单元的单独写入速度。这从单一读取以及单一写入的命令序列来看则能明白这二者皆要执行预充电,但是DRAM单元在写入特性上不必进行预充电,然而,这是为了配合丛发模式以及同列存取而设计成相同的命令序列,所以在SDRAM的传输技术之下,软体对于资料处理的设计也会影响程式码的执行速度。如果电脑软体未能针对丛发模式进行最佳化,但又要提升执行速度,这会有叁种选择,一是超频,二是升级主记忆体,叁是升级PC。

1T DRAM模组的超频性能

如果说3T DRAM是第一代DRAM技术,使用差动放大器实现读取功能的1T DRAM是第二代DRAM,那么在本文中的第叁代DRAM技术是指取代差动放大器且大幅提升读取功能的存取技术。1T DRAM的记忆体单位是由一电晶体以及一电容器所组成的储存单元,又称为1T DRAM单元。图3显示在单一储存单元上进行存取作业的波形,上半部份是使用差动放大器的第二代技术,下半部份是第叁代技术,此图主要用于比较这二者完成读取作业所需花费的最长时间。当这一电容器的储存电压(Vstorage)放电达到最小差异电压(Min. ∆V)时就必须立即进行更新作业(即读取),所以此图呈现有关读取作业的最长时间就等于是更新作业的最长时间。图中标示有tprecharge、tread、trewrite、twrite,这些技术用语依序对应产品规格的tRP、tRCD、CL与CWL。第叁代技术无需tRP,除此之外,tRCD也很短暂且可由CWL替换CL,因此存取速度接近SRAM,存取效率低于SRAM。

图3:单一储存单元进行读取作业的波形

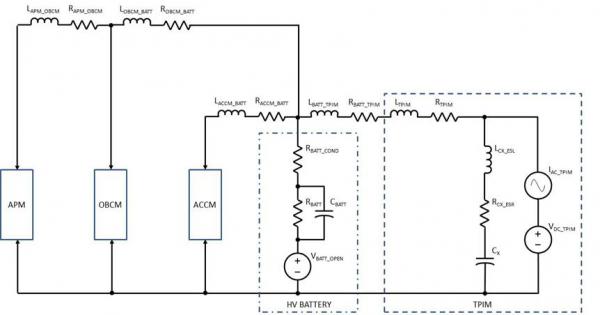

图4用于观察SDRAM的命令序列对于不同存取技术所发生的变化,此图用于比较第二代与第叁代技术之间的存取效率。SDRAM的命令序列有多种组合,其中读取命令至写入命令(READ to WRITE)最能突显不同存取技术之间的差异。第叁代技术的读取时间(tread)很短,于是CL值可以很小,但受到差动时脉讯号以及DQM讯号的限制而不能等于0;另外,即使CL值等于1也还有回写时间(trewrite),所以第叁代技术要以CWL值来替换CL值。

图4:SDRAM的命令序列:读取命令至写入命令

参考叁星电子(Samsung Electronics)产品型号为K4A4G165WD的产品规格表,其中有一规格是DDR4-1600 (11-11-11),时脉时间(tCK)是1.25奈秒(ns),CWL的正常值是9,且小于CL值。时脉时间的倒数是资料传输介面的时脉频率;1600是资料传输介面的传输速度,SDR的传输速度等于时脉频率,DDR的传输速度是时脉频率的2倍;(11-11-11)所对应的定义依序是CL、tRCD、tRP,这些数值合称为速度容器(speed bin)。这容器在PC上就是北桥晶片组内部的组态暂存器,必须在其储存这些数值之后才能存取主记忆体。

在图2中,tRCD以及tRP对应时脉讯号的正缘,因此这二者的最小值是0。在图4中,CL的最小值受到时脉讯号的限制,因此是1;另外,特别标示CWL及其数值在于表示当正常工作时,CWL与tCK相乘之后的数值必须大于或等于储存单元的写入时间(twrite)。当执行超频时,若不增加CWL值则必须更加频繁执行更新命令,除此之外,由于IC的製程变异以及洩漏电流而导致每一储存单元的存取时间不一致,因此更容易发生资料错误,所以为了稳定性而必须增加CL值以及CWL值,甚至要特别降温。当上述这些参数在相同的製造条件之下生产第叁代DRAM技术时,速度容器的最小设定值可以是(1-0-0),CWL值可同于上述的产品规格,因此第叁代DRAM技术的存取效率在尚未超频之时就可超过以第二代DRAM技术所生产的超频记忆体模组。

3T SRAM模组的超频性能

3T DRAM单元是首次实现DRAM的储存单元,为了大幅减小IC的佈局面积而发展到1T DRAM单元。笔者在当年发现微处理器的时脉频率受到DRAM的限制而尝试以叁电晶体组成SRAM,这样的佈局面积大约与3T DRAM单元相似。如果将SDRAM换成同步静态随机存取记忆体(SSRAM),那么在存取效率上是远高于第叁代DRAM的,因为它的CWL值可达到0,在这样的条件之下假使没有丛发模式以及同列存取也能趋近资料传输介面的传输速度。如果使用3T SRAM模组进行超频,那么存取时间会正比于电晶体的切换时间,并且温度升高会减小切换时间,因此CL以及CWL的组态设定值不会因超频而增加,也不必特别降温。

结语

根据研究报告指出,DRAM单元在读取时会发生软错误(soft error)而导致微处理器不能正常执行程式码,所以要求DRAM模组加入错误纠正码(ECC)。那么有谁反向思考过这问题:在微处理器以及晶片组内部也有许多暂存器,为何这些研究报告没有明确指示这些暂存器也要使用ECC来减少软错误呢?

在我们观察第二代DRAM技术在单一储存单元上进行存取作业的波形图之后就能得知差动放大器的鑑别準位非常低,所以比那些暂存器以及SRAM单元更容易受到干扰。超频功能可以增加微处理器的处理速度,但对于大量资料的存取效率则取决于主记忆体的技术,而那些存取性能不佳的主记忆体更容易导致微处理器发生无作业时间(NOP time)来等候存取资料,因此在超频之后有可能增加功率消耗,也难以经由超频功能来大幅提升对于零散资料进行处理的速度。(本文作者——汤朝景,曾任职经济部智慧财产局专利审查委员)

本文由大比特资讯收集整理(www.big-bit.com)

暂无评论