确保高频高速信号完整性的10个关键因素

信号完整性

对于依赖大量持续准确数据流的应用来说,确保信号完整性是至关重要的。比如物联网、工业4.0和相互连接的生态系统。最重要的是,在高比特率和长距离传输的情况下,诸如噪声、失真、插入/回路损耗和串扰等影响可能会使信号失真到发生错误或系统故障的程度。

连接器性能是优异连接的一部分。决定数据传输成功的其它关键因素包括电缆本身的质量和性能,连接器布线和连接设备之间的接口,以及发射和接收装置的质量。平衡布线性能由多个参数定义。最相关的是衰减(插入损耗)、反射(回流损耗)、近端串扰(NEXT)和远端串扰(FEXT)。事实上,电缆连接器组件设计中的每一个决定最终都会影响信号的完整性。

优化高速数据传输的产品、确保信号完整性面临10个关键的设计挑战。

1) Transmission linen. 传输线,波导线

电缆连接的中断会影响信号传输。信号频率越高,损耗就越大。相对传输距离来说,信号的最大需要频率(fMAX)更重要。

2) Signal degradation 信号衰减

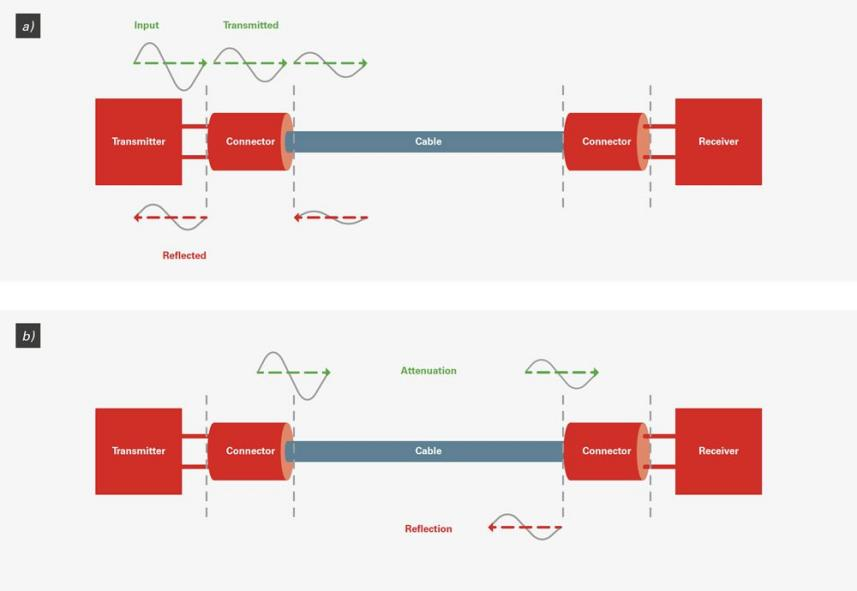

反射和衰减是信号退化的两个主要原因。在传输模块和连接器的交叉点处可能会发生信号退化。如果发射机的输入阻抗与连接器的输入阻抗不同,则部分输入能量将反射到发射机上。由于金属电介质或其它介电质的损失,一些剩余的能量将在连接器中丢失,而波将到达连接器的另一边。反射是连接器信号损耗的最重要原因,而衰减是电缆损耗的主要原因。除了这两种影响外,噪声和串扰也会造成问题。

由于衰减和阻抗不匹配而导致的信号退化:a)发射机侧,b)在电缆和接收机侧。

3) Impedance matching 阻抗匹配

为了优化阻抗匹配(V/I或E/H比值),应考虑所有部件的接触直径、接触间距离、接触形式和材料类型等因素。连接器的设计可能会影响NEXT和FEXT的性能,而且连接器还必须针对这些约束条件进行优化。

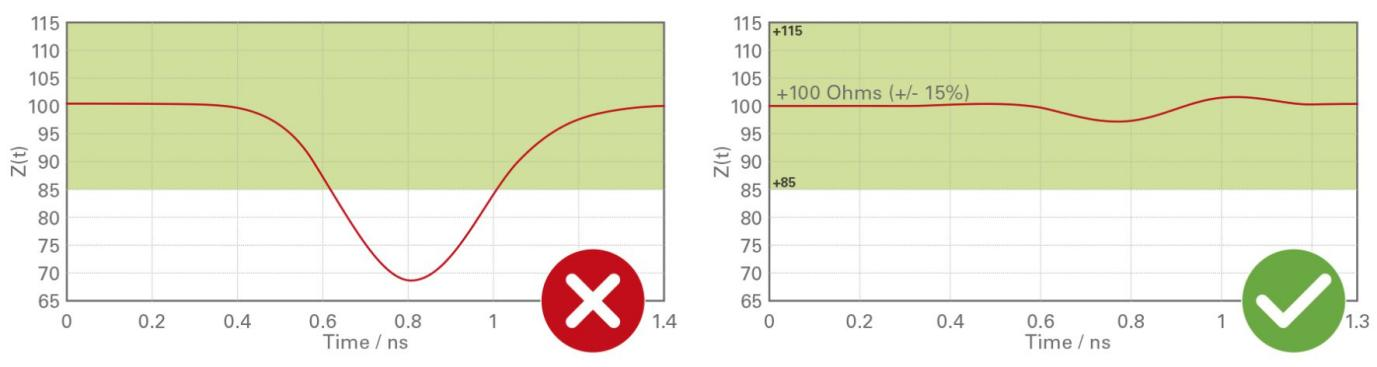

阻抗匹配设计的连接器之间的差异。

4) Crosstalk 信道之间的串扰

重要的是要确定在平行通道中运行的波是否相互作用并引起干扰(串扰)。电缆连接器组件实现物理层中1e-12的通常误码率的参数之一是NEXT和FEXT串扰的水平,即电缆内从一个通道到另一个通道的现场耦合。为了尽量减少串扰,引脚的位置和信号的归因到引脚布局都是至关重要的。

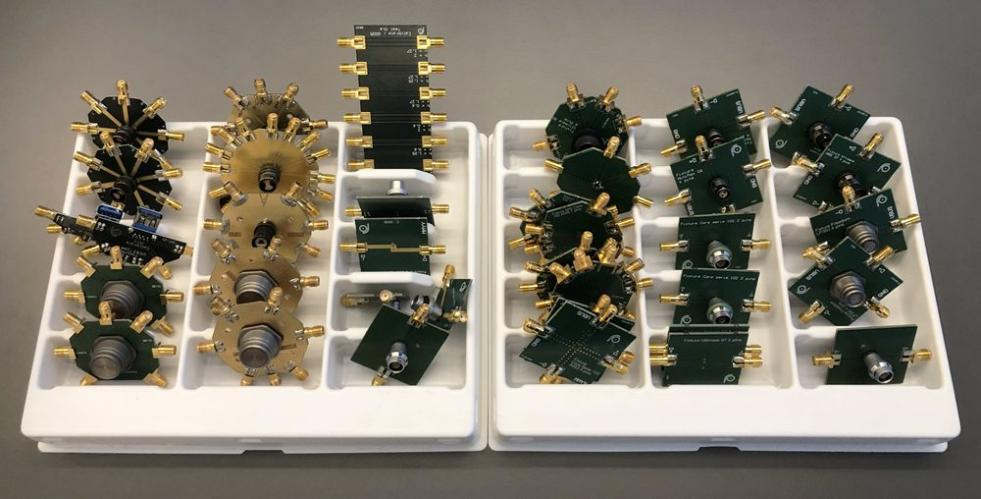

比较在同一连接器中具有不同信号方式的两种串扰。

5) Vector Network Analyzer (VNA)矢量网络分析仪(VNA)

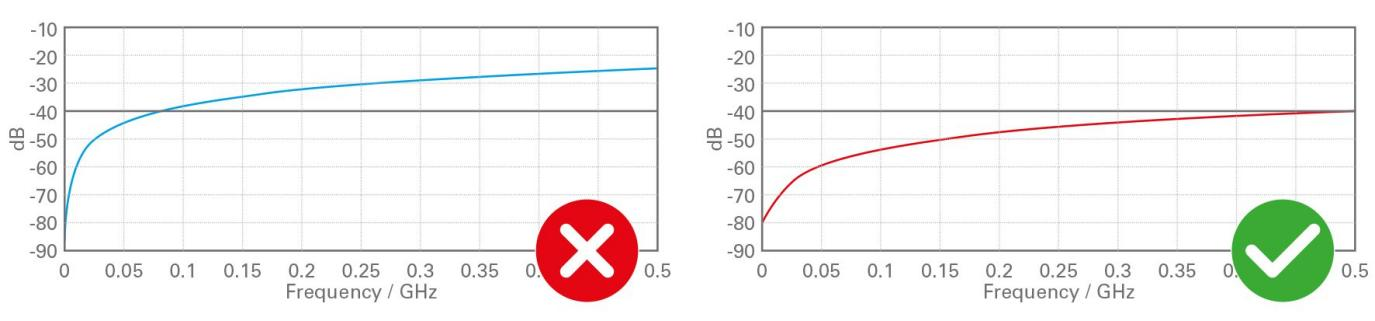

数据协议提供了数据传输参数的规范值(插入损耗、返回损耗、串扰、串扰、噪声),确保系统各组件,包括发射器、接收器、电缆、连接器等的兼容性,以便它们能够适当地一起工作。典型的协议包括以太网、USB、SDI、DP和HDMI。一旦一个设计针对一个已定义的协议进行了优化,就需要测试一个物理连接器以及电缆组装原型,使用向量网络分析仪(VNA)来验证完整的特性。测量组件在电连接上的反射和透射的波参数作为频率的函数,即所谓的散射参数,或s参数。被测试的典型设备没有进行测量所必需的同轴接口,因此测试装置通常需要插入仪器的同轴接口和被测设备(DUT)之间,如PCB、封装、连接器或电缆。要将电缆连接器组件连接到VNA设备,需要根据所需的带宽设计一个高速精密PCB。

VNA测量用PCB固定装置的示例

6) Geometrical optimization形状优化

任何几何实体都可以潜在地改善或干扰连接器从一侧到另一边的能量流。因此,每一个与高速相关的设计都必须针对机械、电气、信号完整性和EMI/EMC性能的所有方面进行交叉优化。需要考虑的主要影响参数是连接器设计、电缆长度、电缆性能(损耗),以及1 Gb/s以上的控制和可重复的电缆组装和封装工艺。

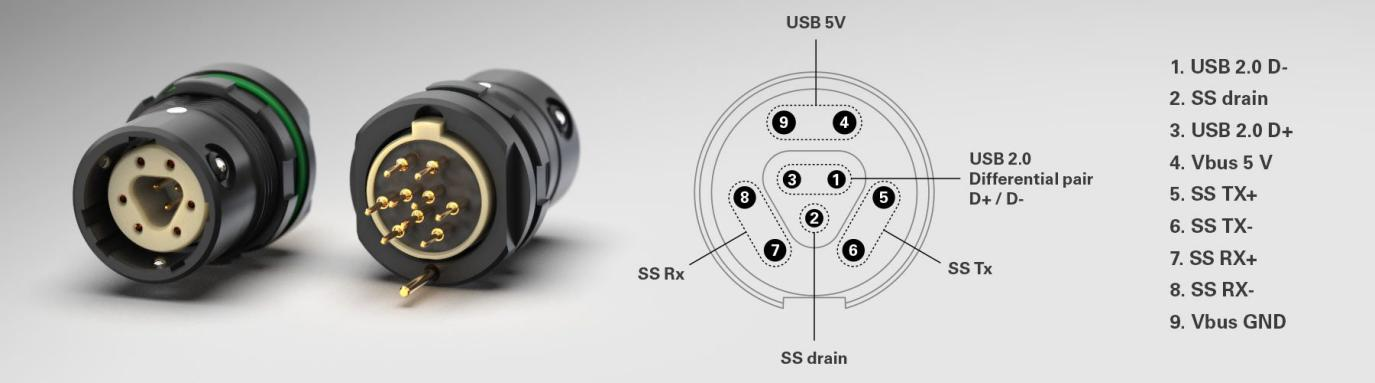

费舍尔MiniMax™系列它被专门设计用于实现使用单一协议(USB3.2)的高速数据传输。

7) Impedance measurement 阻抗测量

通过观察纵向场分布,确保掌握横向电磁(TEM)传播模式后,必须确保正确设计针的直径及其分布,以达到正确的阻抗。连接器的设计可能会影响NEXT和FEXT的性能,而且连接器也必须针对这些约束条件进行优化。对于阻抗测量,可以使用时域反射测量(TDR)设备。

8) De-embedding 去嵌入

必须消除PCB夹具的影响。建议实施IEEE 370-2020标准,确保最佳的PCB制造和工艺。

9) SerDes simulationSerDes SerDes仿真

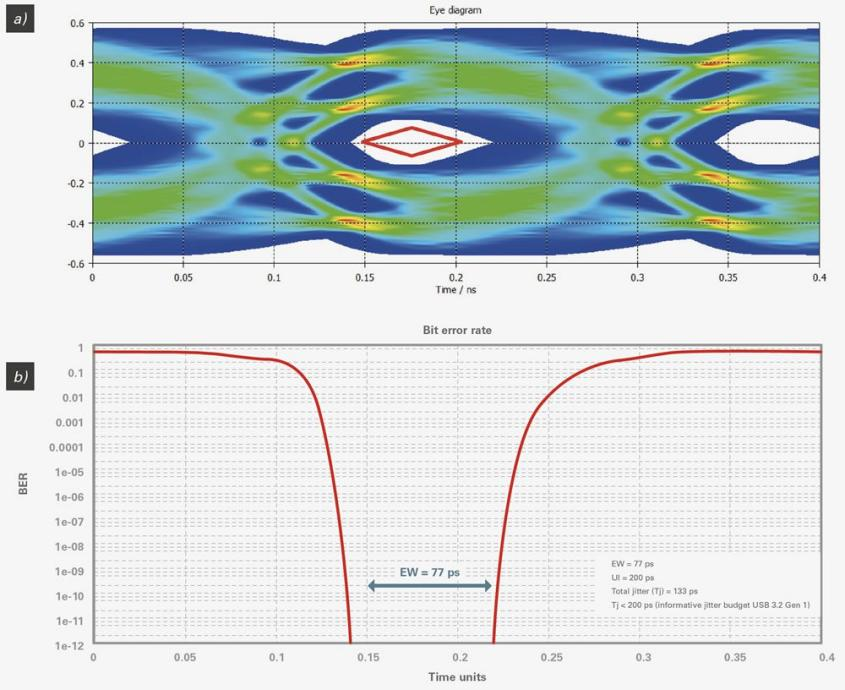

在物理层上通信系统的总体速度取决于物理层的体系结构,以及发射机和接收机的规格。在许多应用中,通信链路的特殊配置可能会偏离标准中的规范。系统级SerDes仿真用于测量电缆和连接器组件的数据传输速率。仿真可以用眼图在视觉中表示,在眼图中,比特的叠加创建一个“眼睛”形状,提供对系统的洞察和关键的连接参数。该图显示了信号传输是否以所需的速生,以及它易受干扰的程度。

5 Gb/s的MiniMax链路模拟:a)眼图显示USB3.2Gen1的最小睁眼率,b)浴缸定时曲线和接收端口的抖动计算。

10) Link optimization链路优化

在许多情况下,通道眼图是关闭的。通过包括信号调节技术,如连续时间线性均衡(CTLE)、决策反馈均衡(DFE)或其它方法打开眼图。

为了优化产品的高速数据传输,防止信号失真,工程师应该从一开始就设计信号的完整性。通过采用一种整体的连接方法(从发射器到接收器),可以避免上述常见的陷阱。还需要在组件和系统级别上彻底测试相关的连接技术。

广告

广告

暂无评论